# Shade: A Fast Instruction-Set Simulator for Execution Profiling

Robert F. Cmelik

Sun Microsystems Laboratories, Inc. 2550 Garcia Avenue Mountain View, CA 94043

David Keppel<sup>†</sup> Department of Computer Science and Engineering University of Washington, FR-35 Seattle, WA 98195

Technical Report UWCSE 93-06-06

## ABSTRACT

Shade is an instruction-set simulator and custom trace generator. Application programs are executed and traced under the control of a user-supplied trace analyzer. To reduce communication costs, Shade and the analyzer are run in the same address space. To further improve performance, code which simulates and traces the application is dynamically generated and cached for reuse. Current implementations run on SPARC systems and, to varying degrees, simulate the SPARC (Versions 8 and 9) and MIPS I instruction sets. This paper describes the capabilities, design, implementation, and performance of Shade, and discusses instruction set emulation in general.

Shade improves on its predecessors by providing their various tracing capabilities together in a single tool. Shade is also fast: Running on a SPARC and simulating a SPARC, SPEC 89 benchmarks run about 2.3 times slower for floating-point programs and 6.2 times slower for integer programs. Saving trace data costs more, but Shade provides fine control over tracing, so users pay a collection overhead only for data they actually need. Shade is also extensible so that analyzers can examine arbitrary target state and thus collect special information that Shade does not "know" how to collect.

# 1. Introduction

Shade simulates (emulates) a processor, and is used to execute and trace programs. Today, Shade runs on SPARC [SPARC8] systems to trace SPEC [SPEC] benchmarks to help build better SPARC hardware and software. Shade cannot yet run operating system code nor multiprocessor applications.

Users write programs, called *analyzers*, which call Shade functions to simulate and trace *applications*, usually benchmarks. The most popular analyzers simulate caches and microprocessor pipelines.

Tracing in Shade is programmable and permits per-instruction access to the state (registers and memory) of the simulated program. Trace information flows from Shade to the analyzer through memory instead of pipes or files. Shade generates traces quickly and the level of tracing detail can be changed while the application is being simulated. Thus, Shade's traces can be recreated on demand, avoiding the processing and storage costs of conventional traces. When conventional traces are desired, it is straightforward to write Shade "analyzers" that generate traces in arbitrary formats.

The system where Shade and the analyzer run is the *host system*. The system where the application runs is the *target system*. The target system need not exist; through simulation, Shade offers applications a *virtual target*

<sup>†</sup> Academic consultant, Sun Microsystems Laboratories, Inc.

Copyright © 1993 University of Washington and Sun Microsystems, Inc. - Printed in U.S.A.

Unlimited copying without fee is permitted provided that the copies are not made nor distributed for direct commercial advantage, and credit to the source is given. Otherwise, no part of this work covered by copyright hereon may be reproduced in any form or by any means – graphic, electronic, or mechanical – including photocopying, recording, taping, or storage in an information retrieval system, without the prior written permission of the copyright owners.

*system* (*virtual machine*). The virtual target may be an incomplete model of the target; for example, Shade does not yet simulate privileged instructions.

Shade uses dynamic compilation to increase simulation performance. At run time, application code fragments are compiled into special-purpose host machine code fragments called *translations*. Translations are executed directly on the host system to simulate and trace the application code. Translations are cached for later reuse to amortize compilation costs.

The translation that Shade compiles for an application instruction is essentially an optimized, in-line expansion of the code a conventional simulator would execute to simulate and trace the same instruction. Some of the work that a conventional simulator must do each time an instruction is simulated, such as fetching and decoding the application instruction, is instead done once by Shade when the translation is compiled. Compiling application instructions in groups provides additional optimization opportunities. For example, virtual application state that would normally be stored and loaded between simulating two application instructions can instead remain in host scratch registers.

Often, the host system is used directly to minimize simulation costs. For example, a target add instruction that sets condition codes can often be simulated with a host instruction that does just the same. This is more efficient than first performing an add, then computing the individual target condition code values based on the target operation, operands and results.

This paper is mostly about the design, implementation, and performance of Shade. The use of Shade is described elsewhere [Cmelik93b, Cmelik93c]. Unless otherwise noted, we are describing the version of Shade which runs Version 8 SPARC applications on Version 8 SPARC hosts.

# 2. User Interface

This section gives a brief tour of the Shade user interface, as seen by the Shade analyzer writer.

## 2.1. Loading

The function shade\_load loads a new application program for simulation and tracing. The arguments to the function are the application program file name, command line argument list, and environment variable list. shade\_load reads the text and data segments from the program file, allocates and clears a BSS (uninitialized data) segment, and allocates a stack, which is initialized from the command line arguments and environment.

Once the application is loaded, the analyzer is allowed to make certain system calls in the context of the application program. For example, the analyzer can make calls that redirect the application's I/O.

Analyzers can (sequentially) simulate multiple applications. This allows analyzers to perform the otherwise painstaking process of summarizing results for multiple-command benchmarks.

## 2.2. Simulating and Tracing

The function shade\_run is called with an array of trace records and the array size. shade\_run simulates the application while filling in trace records. It returns the number of instructions traced, which may be less than the number of instructions simulated. Zero is returned when the application has terminated.

Shade provides analyzers with control over tracing, so analyzers only pay for the trace data they want. Shade can directly record the following trace information:

- · instruction address

- · instruction text

- decoded opcode value

- · effective address: data address for loads and stores, target address for control transfer instructions

- branch taken flag

- annulled (squashed) instruction flag

- values of integer and floating point registers used in the instruction; source register values are recorded before instruction simulation, destination registers after

The analyzer specifies which of these values should be recorded for each opcode. For example, an analyzer that simulates instruction and data caches can direct Shade to record instruction addresses and the annulled instruction flag for all instructions, plus effective memory addresses for loads and stores.

Shade knows how to gather the trace information listed above. Analyzers can gather additional information, such as special purpose register values, by supplying functions that are called just before or just after an application instruction is simulated. Different trace functions may be specified for different opcodes. Trace functions are not called for annulled instructions.

Each trace function is called with two arguments. The first is a pointer to the instruction's trace record, which may be used to store information collected by the trace function. The same trace record also serves to provide the trace function with the standard trace information described above. The second argument to the trace function is a pointer to the application's current virtual state structure, which contains the application's current virtual register values. The trace function may also access the application's "virtual" memory.

User trace functions can amend trace records but can neither create nor destroy them. User trace functions can alter the application's state, but doing so is neither recommended nor reliable.

Analyzers can enable and disable tracing according to instruction address.

The trace control configuration may be changed when Shade is not running the application (i.e. outside shade\_run). This level of control is enough to allow long applications to be sampled, or completely analyzed in stages, with separate stages run in parallel by separate Shade invocations to reduce run time.

Sometimes it is desirable to regain control from shade\_run before it has filled the trace buffer. For example, the user may wish for shade\_run to return immediately before or after running an application system call. Yet if tracing is minimal, the entire application may be run in a single shade\_run call. An analyzer can enable tracing<sup>1</sup> for all instructions, and set the trace buffer size to one instruction. Control then returns to the analyzer after running each application instruction. This is not very efficient, though, due to the overhead of switching between the analyzer and the application.

Conventional debuggers suggest several control mechanisms, including *instruction breakpoints* which would cause shade\_run to stop before or after application instructions by opcode or address, and *data breakpoints* which would cause shade\_run to stop before or after loading or storing data at user specified addresses. More generally, the user could supply functions which would be called during simulation, and, based on the current state of the application, decide whether shade\_run should stop. None of these mechanisms are currently implemented in Shade.<sup>2</sup>

It would also be useful to allow *user simulation* functions, which would let the user modify or extend the base instruction set provided by Shade. No such facility is implemented in Shade.

## 3. Implementation

This section describes some of Shade's implementation details, especially those related to simulating and tracing application programs.

## 3.1. Simulating and Tracing

The function shade\_run is responsible for simulating and tracing application code. At its heart is a small main loop (see Figure 1) that finds and calls a translation corresponding to the current target instruction. The translation is built by cross-compiling the target instruction into host machine code. The translation simulates the target PC, optionally records trace information, and returns to the main loop. In practice, each translation simulates several target instructions before returning to the main loop.

The main loop, translations, and most utility functions which are called by the translations, all share a common register window and stack frame. Several host registers are reserved for special purposes:

<sup>1.</sup> Note that tracing can be "enabled" even if no trace data is actually recorded in the trace buffer entries.

<sup>2.</sup> A Shade analyzer based on the GNU debugger gdb [Stallman87] has been developed for Version 9 SPARC software development [Evans92].

```

initialize registers

continue1:

sll

%vpc,..., %10

! hash application pc ...

srl

%10, ..., %10

! . . .

sll

%10, ..., %10

! ... into tlb offset

ldd

[%tlb + %10], %10 ! tlb lookup (loads %10 and %11)

cmp

%vpc, %10

! tlb hit?

be,a

run

! translation address

%11, %00

mov

807

! no chaining

clr

continue2:

save some registers

mov

%o7, %o1

! chaining address

! returns translation address

call

shade_trans

%vpc, %o0

mov

restore saved registers

run:

check for signals

jmpl

%00, %q0

! jump to translation

nop

eot:

save some registers and return

```

Figure 1. Simulator main loop

- pointer to application's virtual state structure (referred to in code examples as vs)

- base address of application's memory (vmem)

- application's virtual program counter; this is part of the virtual state, but is used enough to warrant its own host register (vpc)

- pointer to current trace buffer entry (tr)

- number of unused trace buffer entries (ntr)

- pointer to TLB (tlb)

Shade locates translations using a table called the Translation Lookaside Buffer (TLB). The TLB associates application instruction addresses with corresponding translation addresses. The main loop does a fast, partial TLB lookup. If that fails, the function shade\_trans performs a slower, full TLB lookup, and if that fails, compiles a new translation and updates the TLB.

Shade then checks for pending signals that need to be delivered to the application. Depending on how the application wishes to handle the signal, Shade may terminate the application at this point, or arrange for invocation of an application signal handler. In the latter case, Shade continues simulating and tracing, but now in the application's signal handler. This process is repeated recursively if another signal arrives while in the application signal handler.

Translations do not return in normal fashion. Instead, they use call instructions to return to one of three points in or about the main loop: eot, continue1, or continue2.<sup>3</sup> Translations transfer control to eot when the trace buffer space is exhausted. Translations transfer control to continue1 or continue2 to pass control to the next translation via the main loop. The two return points are used by the translation compiler to implement an optimization called translation chaining.

<sup>3.</sup> Control transfer is similar to a continuation-passing style, but continuations are compiled into each translation.

### 3.1.1. Translation Chaining

Often, the execution of one translation always follows that of another. The two translations, predecessor and successor, can be directly connected (chained) to save a pass through the main simulator loop.

When the successor translation is generated first, the predecessor translation is compiled with a branch to the successor. Otherwise the predecessor translation is compiled with a call instruction to transfer control to continue2 in the main loop. The call instruction saves its own address, which is later passed to shade\_trans. shade\_trans generates the successor translation, then overwrites the predecessor's call with a branch to the successor, thus chaining the two translations.

Translations for conditional branches are constructed with two separate exits instead of a single common exit, so that both legs may be chained.

Translations for register indirect jumps and software traps (which might cause a control transfer) cannot be chained since the successor translation may vary from one call to the next. For these translations, control transfers to continue1 in the main loop.

Using the continuel return point is more efficient if the next translation has already been generated and appears in the TLB. Using continue2 is more efficient when the partial TLB lookup following continue1 would fail and control would fall through to continue2 anyway.

## 3.1.2. Translations

Application instructions are typically translated in chunks which extend from the current instruction through the next control transfer instruction and accompanying delay slot. Translation also stops at tricky instructions such as software trap and memory synchronization instructions.

Shade arbitrarily limits the number of application instructions per translation (to 1024) in order to simplify storage allocation. The user's trace buffer size also limits translation size. Therefore, a translation may represent more or less than one basic block of application code, and one fragment of application code may be simultaneously represented by more than one translation. The TLB effectiveness is reduced when there are fewer application instructions per translation, or when there are multiple translations for the same application instruction.

Each translation may be broken down into three sections: a prologue, a body with a fragment for each application instruction, and an epilogue.

#### 3.1.3. Translation Prologue

The translation prologue (see Figure 2) allocates trace buffer space for the translation. If there is not enough space, the full-buffer translation return is taken. Prologues are generated only for translations that trace instructions.

Analyzers control the tracing of annulled instructions. When annulled instructions are untraced, the required amount of trace buffer space is not known until the translation is run. For these translations, the prologue allocates enough space to trace the potentially annulled instruction, and the translation body makes the appropriate adjustment if the instruction is annulled.

```

prologue:

subcc %ntr, count, %ntr

bgeu,a body

nop        ! hoist (replace) from body

call eot ! full-buffer return

add %ntr, count, %ntr

body:

```

Figure 2. Translation prologue

The trace space requirements for each translation might instead have been saved in a data structure, and tested by the main loop. This would save the code space now used for translation prologues, but would require executing additional instructions to address and load *count*, and would be inconsistent with translation chaining in which translations branch to each other, circumventing the main simulator loop. Here and elsewhere, the translation compiler *hoists* the target of a branch or call instruction into the delay slot to replace the nop instruction which was originally generated for lack of anything better. The branch or call instruction is then updated to target the instruction following the original target. Control transfer instructions are not hoisted.

#### 3.1.4. Translation Body

The translation body contains code to simulate and optionally trace each application instruction. Simulation consists of updating the virtual state (registers plus memory) of the application program. Tracing consists of filling in the current trace buffer entry and advancing to the next.

# 3.1.4.1. Simulation

Figure 2a shows a sample application instruction, and Figure 2b shows the code generated to simulate it.

Figure 2a. Sample application code

```

ld [%vs + vs_r1], %l1

ld [%vs + vs_r2], %l2

add %l1, %l2, %l3

st %l3, [%vs + vs_r3]

inc 4, %vpc

```

Figure 2b. Translation body (no tracing)

The translation body first loads the contents of application registers r1 and r2 from the application's virtual state structure into host scratch registers 11 and 12. Next, the translation performs the add operation. Then, the translation writes the result in host scratch register 13 back to the virtual state structure location for application register r3. Finally, the translation updates the application's virtual PC.

The code that is generated to actually perform the application operation is very often one and the same instruction, but with different register numbers. Where the host machine is a poor match to the virtual target machine, or where we wish to virtualize the target machine operations, several instructions, or even a call to a simulation function may be used. At the other extreme, no instructions need be generated to simulate useless application instructions (e.g. nop).<sup>4</sup>

Application memory addresses must be translated for loads, stores, and other instructions which access memory. Translation is performed by adding the application memory address to the offset *base address*, stored in host register %vmem. The same offset applies to all application memory address translations.

Note that SPARC supports both register+register and register+immediate addressing modes for memory operations. Often (roughly 30% of the time) one of the target instruction's address operands is zero, and can be replaced by %vmem, which saves an add instruction.

Conceptually, the virtual PC is updated for each application instruction as shown here. In practice, it is only updated in the translation epilogue, or as needed in the translation body for tracing application instruction addresses.

A Delayed Control Transfer Instruction (DCTI) is a control transfer instruction such as a branch, jump, or call instruction, that takes effect only after the dynamically following instruction (which is called the *delay slot*) has been executed. In principle, Shade must maintain both a virtual PC and a virtual NPC (next PC) in order to simulate DCTIs. In practice, Shade is usually able to translate and simulate DCTIs in tandem with the statically following in-

<sup>4.</sup> Shade assumes application nops serve a useful purpose; they are elided only when other instructions, such as simulation or tracing code, are available to replace them.

struction, and the NPC is maintained implicitly as PC+4. When the delay slot is itself a DCTI, or when simulation must be suspended between the DCTI and its delay slot, Shade must simulate the NPC in order to correctly follow the control flow. In these cases, Shade generates the less efficient Shadow translations, which are described below.

#### 3.1.4.2. Tracing

Figure 2c shows the code generated to simulate and partially trace the sample application code. Note that tracing requirements may vary from one application instruction to the next. The tracing code that is generated varies accordingly.

```

st

%vpc, [%tr + tr_pc]

! trace instruction address

set

0x86004002, %00

%00, [%tr + tr_iw]

! trace instruction text

st

ld

[%vs + vs_r1], %11

ld

[%vs + vs_r2], %12

! trace 1st source register

st

%11, [%tr + tr_rs1]

%12, [%tr + tr_rs2]

st

! trace 2nd source register

mov

%vs, %ol

call

pre-instruction trace function

%tr, %00

mov

%11, %12, %13

add

st

%13, [%vs + vs_r3]

%13, [%tr + tr_rd]

! trace destination register

st

%vs, %ol

mov

post-instruction trace function

call

%tr, %00

mov

inc

4, %vpc

trsize, %tr

! advance in trace buffer

inc

```

Figure 2c. Translation body (some tracing)

Instruction trace records have two parts. In the first part, Shade stores trace information it knows how to collect directly. This information is at fixed offsets (tr\_pc, tr\_rs1, etc.) from the beginning of the trace record. Shade stores some adjacent components with a doubleword store instruction, so trace records must be doubleword aligned.

User trace functions may record information in the second part of the trace record. The analyzer specifies an overall (first plus second part) trace record size (*trsize*), which is used to advance the trace buffer pointer.

One feature/kludge is that the first part of the trace record only needs to be long enough to hold the trace information that the analyzer wants Shade to record directly. With this in mind, more popular trace information (like instruction address and text) is located nearer the beginning of the trace record. A more general approach would allow the user to specify the trace component offsets within the trace structure. This approach would complicate the user interface but have negligible impact on compilation and execution.

The trace buffer entry counter (ntr) is decremented once, in the epilogue. Though an increment for the trace buffer pointer (tr) is shown here, it too is generally updated once in the epilogue. The host SPARC store instructions have a 13-bit indexing offset, so  $\lfloor 2^{12}/trsize \rfloor$  trace records are immediately accessible (for simplicity, Shade uses only positive indexing offsets). When greater range is required, the trace buffer pointer is updated by the body as needed.

When a user trace function is called, live application state is first returned to the virtual state structure for use by the trace function. An exception is the virtual PC, which is available in the trace buffer entry.

### 3.1.5. Translation Epilogue

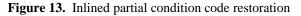

The translation epilogue (see Figure 3) updates the virtual state structure. The epilogue saves host registers that hold modified virtual register values. If the virtual condition codes have been modified, they too must be saved unless, as discussed later, the save can be avoided. The epilogue also updates the trace buffer registers %tr and %ntr if necessary.

Finally, the epilogue returns control to the main loop, or, if the translation is chained, branches directly to the translation which corresponds to the updated virtual PC value. The virtual PC remains in a host scratch register across translation calls. Upon return from a translation, it contains the address of the next application instruction to be executed.

epilogue: update virtual state structure update virtual PC inc count \* trsize, %tr call continuel or continue2 ! return to main loop nop

Figure 3. Translation epilogue

The nop at the end of the epilogue may be replaced by hoisting when the translation is chained.

## **3.2. Shadow Translations**

Shadow translations<sup>5</sup> are generated instead of ordinary translations under the following circumstances:

- 1. to handle DCTI couples

- 2. to handle any DCTI when the analyzer has limited the trace buffer size to a single entry

- 3. to permit synchronous signal handling when an application instruction might trap, and trapping should cause the application's signal handler to be simulated "immediately"

Shadow translations maintain a virtual NPC and an annul-pending flag in addition to a virtual PC. The virtual PC value is set from the virtual NPC value. The new virtual NPC value is set to PC+4 for instructions which don't cause a control transfer; to the target address for call, jmpl, and taken branches; or to the fall-through address for untaken branches. The annul-pending flag is set when the next instruction should be annulled instead of executed.

The SPARC architecture specifies that executing a conditional branch with a DCTI in its delay slot has undefined behavior. For these illegal DCTI couples, Shade silently mimics the "obvious" behavior used in most of today's SPARC implementations.

Since Shadow translations may have different successors from one invocation to the next, they cannot be chained. Ordinary translations, though, can be chained to Shadow translations. Likewise, modified virtual condition codes must always be saved in Shadow translation epilogues because Shade cannot determine whether the application will set them before using them.

#### **3.3. Translation Cache (TC)**

The TC is the memory where translations are stored. In an earlier version of Shade the TC was organized as an array of fixed sized entries, with one entry per translation and one translation per application instruction. The application instruction address mapped directly to the corresponding TC entry.

The old organization was abandoned to allow multiple application instructions, variably traced, per translation. Now translations are simply placed in memory one after the other, irrespective of length, and the TLB associates the application instruction address with the corresponding translation address.

<sup>5.</sup> So called because they resemble the code used in Shadow, Shade's predecessor.

When more TC space is needed than is available, all entries in the TC are freed and the whole TLB is cleared. Since this deletes useful translations, the TC is made large so that freeing is rare. Translation chaining makes other freeing strategies tedious.

The TC and TLB are also flushed when there is any change in the tracing strategy, since tracing is hardcoded into the translations. This is not expected to happen often.<sup>6</sup>

If the application uses self-modifying code, the TC and TLB entries for modified application code will be invalid after the modification. SPARC systems provide the flush instruction to identify code that has been modified; many other systems provide equivalent primitives [Keppel91]. When an application flushes instructions, Shade makes the corresponding translations inaccessible. Note that translations may be reached either through the TLB or through translation chaining. If a flushed application instruction is later executed, a new translation for it is compiled.

To simulate the first flush instruction, Shade frees the TC, flushes the TLB, and disables future translation chaining. To simulate subsequent flush instructions, Shade flushes TLB entries which point to translations for the flushed instructions. Since Shade does not maintain enough information to tell exactly which translations cover which application instructions, TLB flushing is done conservatively, and some TLB entries will be needlessly flushed.

Older SPARC systems with unified instruction and data caches will correctly execute self-modifying code without the need for flush instructions. So applications exist (e.g. the dynamic linker) which don't flush when they modify code. By default, Shade makes TLB entries and chains translations only for application code inside the (read-only) text segment. As a result, instructions such as the dynamic linker (loaded at run time) and the code it loads are recompiled each time they are simulated. A Shade run-time option (-flushbench) may be specified to indicate that the application executes flush instructions where it should.

There are two Shade run-time options which control when Shade itself uses flush instructions. By default, Shade flushes all code that it generates or modifies. The first option (-noflush) tells Shade it need not execute flush instructions. The second option (-flushp) tells Shade to execute a single flush instruction between generating/modifying and executing an arbitrary amount of code.

Full flushing is required, e.g., for MicroSPARC which has split instruction and data caches and requires that software maintain consistency. Full flushing is also required when running Shade on itself. Partial flushing may be used, e.g., for SuperSPARC, which has consistent instruction and data caches, but which doesn't check instructions currently being executed against recently stored data.

## 3.4. Translation Lookaside Buffer (TLB)

The TLB is an array of lists of address pairs. Each pair associates an application instruction address with the corresponding translation address.

To find a translation, Shade hashes the application instruction address to produce a TLB array index. This TLB entry (address pair list) is then searched for the given application address.<sup>7</sup> If the search succeeds, the list is reorganized (if necessary) so that the most recently accessed address pair is at the head of the list. If the search fails, a translation is generated, and a new address pair is placed at the head of the list.

Lists are actually implemented as fixed length arrays, which makes the TLB simply a two-dimensional array of address pairs. The TLB may also be thought of as N-way set associative, where N is the list length. Since address pair lists are of fixed length, it is possible for address pairs to be pushed off the end of a list and lost, which makes the translation inaccessible via the TLB. The TLB is large enough that this is not a problem. The translation will likely also still be accessible via chaining from other translations.

#### 3.5. Optimizing Translations

Shade uses an ad hoc code generator which generates code in roughly one pass. Some minor backpatching is later performed to chain translations and replace nops in delay slots. The resulting code could no doubt be improved,

<sup>6.</sup> Retranslation overhead due to trace control changes could be reduced by caching the translation state (TC, TLB, etc.) by trace control strategy.

<sup>7.</sup> Recall that the main simulator loop only checks the first member of this list.

but the time spent in the analyzer usually dwarfs the time spent in code generation, simulation, and tracing combined. A run-time code optimizer seems unjustified in this case; the cost and potential bugs of a run-time code optimizer should be seriously considered as well.

Optimization is more important when Shade is used for pure simulation with no tracing or analysis. A different tradeoff might be made between the cost of code optimization and the quality of optimized code.

## **3.6.** Conflicts of Interest

The decision to simulate, trace, and analyze all in the same process leads to conflicts over the use of per-process state and resources. Conflicts arise between the application program (i.e. the code generated by Shade to simulate the application), the analyzer, and Shade (translation compiler, etc.). Conflicts are resolved in one or more of the following ways:

- 1. Partition the resource (e.g. memory, file descriptors, signals). Part of the resource belongs to one contender, and part to another. If necessary, interfaces are provided to hide the partitioning, and perhaps provide some protection.

- Time multiplex the resource (e.g. special purpose registers). Part of the time the resource belongs to one contender and part of the time it belongs to another. Additional processing time and storage are required for swapping.

- 3. Simulate (virtualize) the resource, invariably on behalf of the application (e.g. register windows). This is the least efficient approach.

- 4. Unprotected sharing (e.g. current working directory). Changes made by either effect both. This is generally a bad thing and the result of an incomplete implementation.

The following sections describe these approaches in more detail.

## 3.6.1. Memory

The virtual address space is partitioned. It is assumed that both the application and analyzer are free of bugs that would cause untoward memory references.

The analyzer, including the Shade run-time routines, runs as an ordinary program in the lower end of memory. shade\_load places the application elsewhere in memory. The kernel picks the actual location for the application given a maximum size estimate provided by shade\_load.

The application stack is placed near the text segment, just below what would be application virtual memory address 0. Thus, application stacks appear to the application as if they are located at the high end of memory. Application stacks do not enjoy the automatic extension provided by UNIX to real stacks. At some cost, Shade could perform this function.<sup>8</sup> Instead, application stacks are just made large.

Application brk and sbrk system calls (which are called by malloc, etc.) are simulated by allocating space following the application's data and BSS segments.

All application memory addresses are offset by the same amount. Thus, once the addresses requiring translation have been identified, address translation itself is simple. Some places where address translation is required include:

- initialization of the application stack pointer and stack frame

- "fetching" application instructions during translation compilation

- simulation of application loads, stores, etc.

- · simulation of register window overflow, underflow, and flush traps

- simulation of application system calls: arguments and return values may be addresses, and may point to data structures containing addresses

<sup>8.</sup> Catching faults then extending the stack would be unwieldy, given the way signals are now handled, as there would be three potential contenders for rights to SIGSEGV. Automatic stack extension otherwise would be acceptable.

## 3.6.2. Registers

For each translation, host scratch registers are picked to represent target registers. Host register numbers then replace target register numbers in the translated application code. Host registers are lazily loaded from the virtual state structure, then later lazily stored back, but no later than the translation epilogue.

The host registers cache virtual register values from one translated application instruction to the next in order to reduce memory traffic to and from the virtual state structure. When there aren't enough host registers to represent all of the virtual registers used, host registers are reassigned pseudo-randomly.

Currently 15 integer and all 32 floating point host registers are used to hold virtual register values. On average,<sup>9</sup> 29% of application integer register reads require a prior load from the virtual state structure, and 58% of writes require a store. For floating point benchmarks, 4% of floating point register reads require a prior load, and 30% of writes require a store.

These numbers do not reflect the additional loads and stores that accompany calls to user trace functions which expect to find the application register values in the virtual state structure.

Shade itself doesn't perform many floating point operations while simulating or translating, so the virtual floating point registers could (as they once were) be assigned on a long term basis (such as the duration of shade\_run, spanning many translations), instead of a short term basis (a single translation). But user trace functions may wish to perform floating point operations, and may wish to find the virtual floating point register values in the virtual state structure. The obvious compromise, using long term mapping only when no user trace functions have been specified, is still under consideration.

Also under consideration is a similar scheme in which high use integer registers (e.g. the stack and frame pointers) are mapped longer term.

Special-purpose registers such as the y multiply/divide register, and the fsr Floating-point State Register are multiplexed. Swapping tends to be relatively infrequent because Shade does not use these registers as often.

## 3.6.3. Integer Condition Codes

The integer condition codes are multiplexed. As application code is compiled, Shade keeps track of whether or not the host condition codes currently represent (contain) the virtual condition codes. Functions described below are used to transfer host condition code values to or from the virtual state structure as necessary. Since these transfers are expensive, attempts are made to limit them.

The condition codes are restored from the virtual state structure only if the application code uses the condition codes before setting them. Here "use" of condition codes includes calls to user trace functions, which might wish to read the condition codes from the virtual state structure. On average, the condition codes only need to be restored for 18% of the application instructions which use them.

Condition codes are not always saved by the translation epilogue. Shade can sometimes determine that the next application code to be executed will always set the condition codes before using them. On average, the condition codes only need to be saved for 7% of the application instructions which set them.

Shade's condition code optimization is unsafe in one special case related to signal handling. When a signal is delivered, the current condition code values are copied from the virtual state structure into a signal context structure. This structure may be examined or modified by the signal handler. The condition codes are updated from this structure when the signal handler returns. Shade sometimes discards condition codes between translations, so values copied into the signal context structure may be unreliable. Signal handlers usually ignore the saved condition codes, because most asynchronous signals are delivered when the condition codes are already unpredictable. However, a signal handler could use the saved condition codes (or, equivalently, set new condition code values in terms of the old values), and in this special case the condition code optimization is unsafe. Shade's -ssignal flag will ensure that signal handlers receive correct condition code values, but it will also reduce performance. Note that condition code restoration is reliable if the signal handler leaves by calling longjmp or siglongjmp.

Unfortunately, in Version 8 SPARC, user instructions cannot directly read and write the Processor State Register that contains the integer condition codes. Figure 4 shows a function which reads the condition codes by exe-

<sup>9. &</sup>quot;On average" here and below means geometric mean of dynamically weighted values over the SPEC89 benchmarks.

cuting conditional branches. Each conditional branch tests one bit in the host condition codes. If the bit is set, the branch is taken, and an instruction in the delay slot records that the bit was set. If the bit is clear, the branch is not taken, and the instruction in the delay slot is not executed.

| shade_geticc:   |                            |

|-----------------|----------------------------|

| clr %00         |                            |

| bneg,a 2f       | ! if negative, assume Z==0 |

| or %00,0x       | 40, %o0 ! N - negative     |

| be,a 2f         |                            |

| or %00,0x       | 20, %o0 ! Z - zero         |

| 2: bvs,a 3f     |                            |

| or %00,0x       | 10, %o0 ! V - overflow     |

| 3: bcs,a 4f     |                            |

| or %00,0x       | 08, %o0 ! C - carry        |

| 4: retl %o7 + 8 | , %g0                      |

| stb %00,[%      | vs + vs_icc]               |

|                 | /                          |

Figure 4. Saving condition codes

Since there are 4 condition code bits, there are a total of 16 possible condition code combinations. The condition codes are written by executing one of 16 code fragments<sup>10</sup> which are specially designed to recreate the condition codes (see Figure 5). The value of the condition codes is used as an index into a table of code fragments where each fragment is 2 instructions (8 bytes). The internal representation for the condition codes (established by shade\_geticc) was chosen to save a 3-bit shift in shade\_seticc. Four of the condition code combinations, those with both the zero and negative bits set, cannot be produced by user instruction sequences. If they are encountered by shade\_seticc, Shade will terminate with a diagnostic.

#### 3.6.4. I/O (File Descriptors)

File descriptors (small numbers returned by the kernel to represent open files or I/O devices) are partitioned between the analyzer and application. Several file descriptor values are special: 0, 1, and 2 represent standard input, output, and error output. Shade renumbers the application's file descriptors so that the application sees the special values even though Shade uses different values.

Shade maintains a table that associates virtual (application) file descriptors with real file descriptors. Shade intercepts each application system call that uses or returns file descriptors, and performs renumbering and table updates as needed. The file descriptor mapping mechanism is available to the analyzer so that it can conveniently control the application's I/O.

Since Shade does not currently retain control across a successful application exec system call, there will be no Shade around after the exec to renumber file descriptors. So prior to the exec, Shade moves the virtual file descriptors to their real locations. Should the exec fail, the file descriptors are moved back. Shade should arrange for analyzer files to be closed on application execs, and application files to be closed on analyzer execs, but doesn't. The analyzer can arrange this if necessary.

## 3.6.5. Signals

Signals can arise for a variety of reasons, and can be delivered either to the application or the analyzer. Signals may also arrive at any time, during execution of Shade, the translations, or the analyzer. Note that in Shade, signals are handled according to ownership rather than time of delivery or cause.

Shade does not reserve any signals, so an analyzer can handle any signal it wishes. Analyzers typically use signals for checkpointing and sampling. All signal numbers are special, and analyzers and applications may use some of the same signals (e.g. hangup, interrupt, alarm clock). Shade prevents applications from interfering with

<sup>10.</sup> The instruction sequences were discovered by brute force search of condition code setting operations and a small set of promising operand values.

```

shade_seticc:

1db

[%vs + vs_icc], %o0

set

lf, %ol

jmpl

%o1 + %o0, %g0

%g0, 1, %o1

sub

1:

retl; addcc %g0, 1, %g0

! ----

retl; subcc %q0, %o1, %q0

! ---C

retl; taddcc %g0, 1, %g0

! --V-

retl; tsubcc %g0, %o1, %g0

! --VC

retl; addcc %g0, 0, %g0

! -Z--

retl; addcc %o1, 1, %g0

! -Z-C

retl; tsubcc %01, %01, %g0

! -ZV-

retl; taddcc %o1, 1, %g0

! -ZVC

retl; addcc %g0, %o1, %g0

! N---

retl; addcc %o1, %o1, %g0

! N--C

retl; taddcc %g0, %o1, %g0

! N-V-

retl; taddcc %o1, %o1, %g0

! N-VC

ba badicc; nop

! NZ--

ba badicc; nop

! NZ-C

ba badicc; nop

! NZV-

ba badicc; nop

! NZVC

```

Figure 5. Restoring condition codes

the analyzer's signal handling. Where possible, Shade arranges to do so in a way that the application doesn't notice.

Shade intercepts sigvec system calls made by the analyzer and records the given signal number. The analyzer then retains exclusive rights to that signal for the remainder of the analyzer run. All signal-related system calls made by the application are intercepted. Shade silently subverts any application requests that would impact the signal handling state (signal handler and flags, blocked signal mask, signal stack) of analyzer-owned signals.

Analyzer signals and their handling are usually invisible to the application, but they can interrupt an interruptible application system call, even when the application has arranged for that signal to be blocked or ignored. Unfortunately, restarting the application system call would be difficult or impossible in most cases.

Signals destined for the application are delivered to a Shade signal handler that notes the signal, and returns control to the interrupted instruction. Eventually, control returns to the main loop, which checks for pending signals. When the main loop detects a signal, it invokes the signal handler instead of the next instruction.

When a signal is delivered, chaining is turned off entirely to reduce the signal handling latency for future signals. The TC and TLB are flushed. Translation chaining is disabled so that a test for pending signals can be made between each translation. A Shade run-time option (-asignal) allows the user to disable chaining from the beginning to prevent a delay in handling the first signal to arrive.

Signals arising directly from the execution of an application instruction (e.g. loading or storing unmapped or unaligned data, or division by zero) can often be handled correctly if they occur in Shadow translations. In these cases, Shade will abort execution of the translation, redirect control to the main simulator loop, and signal handling will proceed as described above. Otherwise, a diagnostic is printed for these signals and the faulting instruction is re-executed, which causes the program to terminate since the signal that would be raised is blocked. A Shade runtime option (-ssignal) causes Shade to always compile Shadow translations.

Shade ignores the execute permissions associated with application code in memory. If the application code is unreadable, Shade will fault as it reads the code, as it attempts to compile a translation.

## 3.6.6. Register Windows

SPARC's windowed register file cannot be partitioned (some windows for the application, some for the analyzer) at the user level. The register file could have been multiplexed at some cost involving system calls and/or window overflow and underflow traps. The simplest solution seems to be to consign the host register file to Shade and the analyzer, and simulate the register file as it is used by the application. It is particularly desirable to avoid application window overflow and underflow traps if/when Shade is run on a bare machine with a kernel as the application.

Shade simulates a register file with one window. Therefore, every save causes an overflow and every restore causes an underflow. Register values are transferred between the virtual state structure and the appropriate save area on the application's stack.

An interesting alternative might be to simulate a virtually infinite register file. In this case the virtual state structure would be huge and no save instruction would cause an overflow, nor restore instruction an underflow. However, we estimate that, on average, this scheme would save only about 0.2 host cycles per simulated application instruction.

User code is rarely conscious of the number of register windows, but system code pays particular attention to it. It is expected that if kernel applications are someday run under Shade, that the analyzer will be able to specify the number of register windows.

#### 3.6.7. Fork, Exec, and Wait

Shade handles an application fork system call by executing a fork system call. This produces two separate processes, parent and child, each containing a copy of Shade, the analyzer, and the application.

In the parent process, a parent application process is simulated, traced, and analyzed; in the child process, a child application process is simulated, traced, and analyzed. Unless other arrangements are made, the separate copies of the analyzer cannot share information, and may conflict with each other. A typical problem is that each copy of the analyzer writes results to the same file.

Application vfork system calls are converted to fork system calls, which may cause some applications to fail under Shade.

Shade handles an application exec system call by executing that system call. Shade, the analyzer and the application are all overwritten by the new application program. Shade might have arranged for a new copy of Shade and the analyzer to be started to simulate, trace, and analyze the new application, but doesn't. Or, Shade might have arranged for the new application to overlay the old application (as if shade\_load had been called), but doesn't. So the new application must be able to run native on the host system.

Shade handles an application wait system call by executing that system call. Both the application and analyzer may have outstanding child processes. Unless the process is waited for by specific process ID, these processes are indistinguishable and the analyzer may complete a wait for the application's process, or vice versa.

One possible solution to this would be to intercept analyzer and application fork system calls and (in the parent) record who made the call, along with the returned child process ID. Application and analyzer wait system calls would also be intercepted. If, say, a wait made by the analyzer yielded information about an application's process, that information would be recorded against a future wait system call by the application, and the analyzer's wait would be retried. Integrating this scheme with SIGCH[I]LD signal handling might be messy.

#### 3.6.8. Resource Limits

Shade simulates application getrlimit and setrlimit system calls to prevent the application from modifying the analyzer's resource limits (maximum CPU time, etc.). However, shade does not attempt to enforce the application's resource limits; Shade just maintains a copy of the analyzer's resource limit values for the application to manipulate.

Before Shade executes an application exec system call, the application's resource limits are installed as the real resource limits, except that Shade refuses to reduce the maximum (hard limit) value for any resource limit. If the exec fails, the previous resource limits are reinstated.

## 3.6.9. Other Conflicts

The following per-process state or resources are shared between Shade, the analyzer, and the application without special handling.

- process ID and parent process ID

- real and effective user and group IDs, and supplementary group IDs; for simplicity and security, Shade refuses to load setuid or setgid applications

- · process group, TTY process group, session ID, and control terminal

- file creation mode mask

- · current working directory and root directory

- scheduling priority

- interval timers

- resource usage (CPU time used, etc.)

- anything to do with System V IPC messages, semaphores, or shared memory

- ptrace flag

# 4. Performance

In this section we give measurements for various configurations running various programs. The *standard organization* used in many of the following tests is:

- The TC holds 2<sup>20</sup> instructions (4MB).

- The TLB contains  $2^{13}$  (8K) lines, each containing 4 address pairs (256KB).

The benchmarks used for this section are the SPEC89 001.gcc1.35 and 015.doduc benchmarks. They were compiled using SPARC Compilers 1.0 with the options:

-cq89-04-libmil-dalign

The tests were run on a SPARCstation 2.

Six Shade analyzers, each performing a different amount of tracing, were used:

icount0

no tracing, just application simulation (The application runs to completion in one call to shade\_run.)

## icount1

no tracing, just update the traced instruction counter (%ntr) to permit instruction counting

icount2

trace PC for all instructions (including annulled); trace effective memory address for non-annulled loads and stores (This corresponds to the tracing required for cache simulation.)

icount3

same as icount2 plus instruction text, decoded opcode value, and, where appropriate, annulled instruction flag and taken branch flag

# icount4

same as icount3 plus values of all integer and floating point registers used in instruction

## icount5

same as icount4 plus call an empty user trace function before and after each application instruction

The analysis performed by each of these analyzers consisted solely of counting the number of instructions executed. In a realistic analyzer, analysis would dominate the run time.

Figure 6 shows how much slower applications run under Shade than they run native (directly on given hardware). The *inst* column shows the number of instructions that were executed per application instruction. Instruction counts were gathered by running the Shade *icount1* analyzer on Shade running the indicated analyzer on the indicated benchmark. The *time* column shows the CPU (user + system) time ratio.

|       | icount0   | icount1   | icount2    | icount3     | icount4     | icount5     |

|-------|-----------|-----------|------------|-------------|-------------|-------------|

| app   | inst time | inst time | inst time  | inst time   | inst time   | inst time   |

| gcc   | 5.51 6.13 | 5.85 6.60 | 8.84 14.32 | 13.50 21.71 | 15.51 31.21 | 63.74 84.17 |

| doduc | 2.75 2.84 | 2.94 3.14 | 5.52 8.78  | 9.44 14.03  | 11.45 24.06 | 36.25 60.30 |

Figure 6. Dynamic expansion: instructions and CPU time

Figure 7 shows how much larger dynamically (i.e. weighted by number of times executed) a translation is than the application code it represents. The sizes are in instructions. Since portions of most translations are conditionally executed, the translation code space expansion values shown in this table are typically larger than the executed code expansion values shown in the previous table. For icount0 and icount5 on *gcc*, a larger share of the instructions are executed outside of the TC in the translation compiler, simulation functions, and the analyzer.

|       | input |           |           | 01        | utput size  |             |             |

|-------|-------|-----------|-----------|-----------|-------------|-------------|-------------|

| app   | size  | icount0   | icount1   | icount2   | icount3     | icount4     | icount5     |

| gcc   | 5.1   | 20.1 4.7x | 25.5 6.2x | 40.6 9.1x | 66.8 14.8x  | 76.9 16.7x  | 192.8 39.9x |

| doduc | 12.5  | 33.2 4.1x | 38.7 5.1x | 73.2 8.0x | 126.0 13.2x | 152.5 15.1x | 427.0 38.6x |

Figure 7. Code translation expansion

Figure 8 shows the percentage of total run time spent in various phases of execution. *Compiler* is the time spent in the translation compiler. *TC* is the time spent executing code in the Translation Cache itself. *Sim* is the time spent in functions which are called from the TC to simulate, or assist in simulating application instructions. *Analyzer* is time spent in the user's analyzer, including user trace functions which are called from the TC. This information was obtained with standard profiling (cc -p; prof). The standard TC and TLB size and organization were used.

The time distribution is a factor of several things. Better optimization takes longer and produces faster running code, both of which increase the percentage of time spent in code generation. A small TC increases the frequency with which useful translations are discarded. A small or ineffective TLB increases the frequency with which useful translations are lost. Translations that collect a lot of information take longer to run, and thus reduce the percentage of time spent in simulation functions, even though their absolute running time is unchanged. All of the analyzers are trivial, though icount5 supplies null functions that are called before and after each application instruction.

| app   | location | icount0 | icount1 | icount2 | icount3 | icount4 | icount5 |

|-------|----------|---------|---------|---------|---------|---------|---------|

|       | Compiler | 8.77%   | 10.14%  | 5.82%   | 4.59%   | 3.86%   | 25.05%  |

|       | TC       | 51.13%  | 52.56%  | 74.62%  | 82.22%  | 86.33%  | 61.26%  |

| gcc   | Sim      | 39.00%  | 36.09%  | 19.01%  | 12.83%  | 9.55%   | 4.97%   |

|       | Analyzer | 0.00%   | 0.03%   | 0.01%   | 0.00%   | 0.00%   | 8.61%   |

|       | Compiler | 0.22%   | 0.35%   | 0.16%   | 0.11%   | 0.08%   | 0.06%   |

| doduc | TC       | 80.69%  | 81.56%  | 91.50%  | 95.20%  | 96.37%  | 87.87%  |

| doduc | Sim      | 19.04%  | 17.97%  | 8.32%   | 4.67%   | 3.55%   | 2.11%   |

|       | Analyzer | 0.00%   | 0.07%   | 0.00%   | 0.00%   | 0.00%   | 9.96%   |

Figure 8. Run-time execution profile summary

Figure 9 shows the frequency of TC flushes. The frequency is a function of the TC size and indirectly a function of the rate at which translations are lost from the TLB. The data in Figure 9 was collected with varying TC sizes and the standard TLB size and configuration. The standard configuration is shown in **bold**.

Figure 10 shows the TLB behavior under various configurations.

• Each program is run with the translation chaining optimization turned on and off. The *Ch* column contains "Y" if translation chaining is turned on.

| app   | TC size | icount0 | icount1 | icount2 | icount3 | icount4 | icount5 |

|-------|---------|---------|---------|---------|---------|---------|---------|

|       | 256KB   | 1338    | 1952    | 4120    | 10862   | 13801   | 110389  |

|       | 512KB   | 366     | 656     | 1344    | 2878    | 3582    | 20767   |

| gcc   | 1MB     | 4       | 50      | 377     | 1060    | 1244    | 5306    |

|       | 2MB     | 0       | 0       | 5       | 197     | 317     | 1628    |

|       | 4MB     | 0       | 0       | 0       | 0       | 2       | 539     |

|       | 256KB   | 5       | 5       | 27370   | 159152  | 164258  | 261997  |

|       | 512KB   | 0       | 0       | 1       | 6123    | 10820   | 27332   |

| doduc | 1MB     | 0       | 0       | 0       | 1       | 1       | 10949   |

|       | 2MB     | 0       | 0       | 0       | 0       | 0       | 17      |

|       | 4MB     | 0       | 0       | 0       | 0       | 0       | 0       |

Figure 9. TC/TLB flushes per 10<sup>9</sup> application instructions

- Each program in Figure 10 was run with several TLB sizes and organizations. The standard configuration is shown in **bold**. Each TLB entry consists of a 4 byte virtual machine address and a corresponding 4 byte host machine address. So the amount of memory consumed is 8 times the number of entries shown in the *TLB Entries* column.

- The TLB associativity was also varied, with the TC size held constant.

- The average search length (*Len* column) shows how many entries on a line are examined to discover a hit or a miss. For a direct-mapped TLB, the search length is trivially one. For associative organizations, the average search length is dominated by the optimization that moves recent hits to the front of each TLB line. When a translation is moved to the front of the TLB line, it is usually used several times before it is displaced. Since the miss rate is low, the average search length for hits is almost identical to the overall search length.

For a fixed-size TLB, increasing the associativity reduces the conflict rate. For example, a fully-associative TLB with this protocol would only replace entries when the TLB line was full, and the least recently used entries would be replaced. However, increasing the associativity increases the number of translations that map to a given line. That increases the probability that two "active" translations will map to the same line and thus contend for the first slot in the TLB.

Note that the main loop can efficiently check the first TLB slot, but if this fails, a relatively expensive call to shade\_trans must be made to complete the TLB lookup.

- The miss rate (*Miss* % column) is the percentage of TLB lookups that failed. On each miss, a new translation is compiled. There are always at least as many misses as there are basic blocks (translations) in the program. The number of misses increases when cached translations are deleted from the TLB to make space for new translations.

- For each TLB miss, a new translation is compiled and entered in the TLB. The replacement rate (*Lost* % column) is the percentage of new translations that cause other translations to be discarded. The replacement rate is affected by the TLB associativity, and the TC flush rate (since the TLB is flushed along with the TC). For these experiments, the TC was never flushed. If the replacement rate were 0% then all misses could be attributed to executing code that hadn't been executed before. If the replacement rate were 100% then all misses could be attributed to TLB conflicts. A high replacement rate means that translations are being recompiled frequently.

Typically, more than 90% of the replaced translations are needed again later, causing recompilation. Greater associativity or a secondary "TLB victim cache" [Jouppi90] could reduce replacement and thus recompilation.

• The translation chaining optimization reduces the number of TLB references. The miss rate increases because translation lookups always miss when the translation is first referenced (cold misses) and because the number of TLB references goes down. However, the absolute number of misses and replacements stays nearly the same. Chaining reduces the demand for TLB entries, which tends to reduce the number of lost TLB entries. The average search length improves, however, because only unchainable, hence fewer, translations are competing for the head of the list.

Figure 11 shows the average number of instructions that are executed by the code generator in order to generate one machine instruction. The number of instructions per instruction in the code generator is a function of the instruction set architecture of the host and target machines and the level of optimization. The statistics were collect-

|       |         |                |             | 4-    | Way Ass   | oc        | 2-    | Way Ass   | ос        | Direc     | t Map     |

|-------|---------|----------------|-------------|-------|-----------|-----------|-------|-----------|-----------|-----------|-----------|

| app   | Ch<br>? | TLB<br>Entries | TLB<br>Refs | Len   | Miss<br>% | Lost<br>% | Len   | Miss<br>% | Lost<br>% | Miss<br>% | Lost<br>% |

|       | Ν       | 16K            | 244M        | 1.097 | 0.091     | 3.130     | 1.037 | 0.105     | 4.061     | 0.445     | 4.503     |

| gcc   | Ν       | 32K            | 244M        | 1.063 | 0.102     | 0.650     | 1.033 | 0.097     | 2.926     | 0.451     | 4.408     |

|       | Ν       | 64K            | 244M        | 1.048 | 0.104     | 0.048     | 1.028 | 0.103     | 0.981     | 0.469     | 4.338     |

|       | Y       | 16K            | 31M         | 1.032 | 0.716     | 0.842     | 1.008 | 0.654     | 1.479     | 0.562     | 3.000     |

| gcc   | Y       | 32K            | 31M         | 1.015 | 0.806     | 0.116     | 1.005 | 0.761     | 0.475     | 0.685     | 1.651     |

|       | Y       | 64K            | 31M         | 1.007 | 0.819     | 0.012     | 1.002 | 0.808     | 0.099     | 0.758     | 0.868     |

|       | Ν       | 16K            | 103M        | 1.023 | 0.003     | 0.001     | 1.014 | 0.004     | 1.297     | 0.039     | 2.786     |

| doduc | Ν       | 32K            | 103M        | 1.015 | 0.003     | 0.000     | 1.012 | 0.003     | 0.009     | 0.038     | 2.744     |

|       | Ν       | 64K            | 103M        | 1.012 | 0.003     | 0.000     | 1.012 | 0.003     | 0.003     | 0.038     | 2.744     |

|       | Y       | 16K            | 7.8M        | 1.000 | 0.037     | 0.001     | 1.000 | 0.037     | 0.058     | 0.035     | 0.520     |

| doduc | Y       | 32K            | 7.8M        | 1.000 | 0.037     | 0.000     | 1.000 | 0.037     | 0.009     | 0.036     | 0.378     |

|       | Y       | 64K            | 7.8M        | 1.000 | 0.037     | 0.000     | 1.000 | 0.037     | 0.003     | 0.037     | 0.370     |

Figure 10. TLB behavior

ed by running Shade on Shade, profiling just the code generator to determine the number of instructions executed in the code generator, and by having the profiled Shade report the number of instructions that it generated.

| app   | icount0 | icount1 | icount2 | icount3 | icount4 | icount5 |

|-------|---------|---------|---------|---------|---------|---------|

| gcc   | 179.7   | 171.25  | 127.2   | 94.0    | 87.5    | 51.4    |

| doduc | 245.4   | 271.2   | 162.6   | 111.9   | 102.1   | 58.9    |

Figure 11. Code generator instructions per instruction generated

#### 5. Cross Shades

In the previous section we focused on the Shade (subsequently referred to as Shade-V8.V8) for which the host and target architectures were both Version 8 SPARC, and for which the host and target operating systems were both SunOS 4.x [SunOS4]. Four other Shades have been developed. The first (Shade-MIPS.V8) runs UMIPS-V [UMIPSV], MIPS I [Kane87] binaries, and the second (Shade-V9.V8) runs SunOS 4.x, Version 9 SPARC [SPARC9] binaries. The host system for both is SunOS 4.x, Version 8 SPARC. There are also versions of Shade-V8.V8 and Shade-V9.V8 where both the host and target operating systems are Solaris 2.x [SunOS5].

All of these Shades are at least complete to the extent that they can run SPEC89 binaries compiled for the respective target systems.

## 5.1. Shade-MIPS.V8

Shade-MIPS.V8 was developed to provide the custom tracing capabilities of Shade for MIPS binaries. Given Shade-V8.V8 and ready access to SPARC systems, SPARC was the natural choice for host architecture.

Little attention was paid to simulation efficiency, beyond the efficient simulation techniques already used in Shade. Also, Shade-MIPS.V8 only simulates instructions and system calls used in SPEC89 binaries. On average, Shade-MIPS.V8 executes about 10 SPARC instructions to simulate a MIPS instruction. We wouldn't expect more than a factor of two increase in simulation efficiency to be easily achieved with Shade.

As a rule, MIPS instructions are straightforward to simulate with just a few SPARC instructions. This is possible because both the MIPS and SPARC architectures are RISC architectures, both support IEEE arithmetic, and the MIPS architecture lacks integer condition codes. The rest of this section describes some of the remaining difficulties, solutions, and compromises.

Though MIPS systems support both big-endian and little-endian byte ordering [James90], SPARC only supports the former. The simulator currently runs only code that has been compiled for MIPS systems running in bigendian mode. To support little-endian byte ordering, Shade-MIPS.V8 would have to reform the data for multibyte loads and stores, which would significantly increase the cost of these instructions.

A similar swapping problem exists for floating point registers. The most significant half of double precision register number N is numbered N+1 on MIPS and N on SPARC. Shade-MIPS.V8 must translate floating point register numbers accordingly.

The immediate field size for common operations is 16 bits for MIPS, but only 13 bits for SPARC. Where target immediates do not fit in 13 bits, one or (most likely) two SPARC instructions are used to place the immediate value in a host scratch register.

The MIPS integer divide instructions perform a divide which provides a remainder. SPARC integer divide instructions aren't implemented in hardware on older systems, and don't provide a remainder. Shade-MIPS.V8 simulates integer divide by calling the standard divide and remainder library functions.

In place of integer condition codes, the MIPS architecture employs values stored in general purpose integer registers. This frees Shade-MIPS.V8 from multiplexing condition codes as is done when simulating SPARC instructions. Some MIPS instructions assign values to registers based on comparison results or branch based on a register value. Shade simulates them in the obvious way, using SPARC compare, conditional branch, and set instructions.

For signed integer add and subtract instructions, Shade-MIPS.V8 does not check for overflows that would cause exceptions on MIPS systems.

The MIPS unaligned memory operations (load/store word left/right) have no equivalents in SPARC instructions and are simulated by calls to special-purpose functions.

The MIPS floating point control register is very similar to the SPARC floating point status register, a fortunate result of IEEE arithmetic support. The bits are arranged differently though, and translations must be performed.

The MIPS floating point instructions which convert floating point to integer values respect the current rounding mode, but the corresponding SPARC instructions always round towards zero. So these MIPS instructions are simulated by calling a math library function.

The object file formats differ between SVR4 and SunOS 4.x, so a different, more complicated, program file reader is required.

Shade-MIPS.V8 intercepts all the application's system calls. Many of the SVR4 system calls have direct equivalents under SunOS. Some have evolved, leaving behind compatibility functions (e.g. signal and time) which are suitable for simulation purposes. Some system calls require data translation of varying complexity, for instance stat (easy) or ioctl (hard and virtually unimplemented). Fortunately, less portable system calls are less likely to appear in benchmarks.

### 5.2. Shade-V9.V8

Shade-V9.V8 simulates a V9 SPARC target and runs on a V8 SPARC host. The principal problems of simulating V9 applications on V8 hosts are wider integer registers and additional condition codes. Simulating a 64-bit address space would be a problem, but so far it has been avoided. The new V9 instructions themselves do not present much in the way of additional problems, although there are a lot of additional instructions. Shade-V9.V8, like Shade-V8.V8, currently simulates only user-mode instructions.

As a rough measure of relative *simulation* complexity, consider that, given Shade-V8.V8, it took about 3 weeks to develop Shade-MIPS.V8 and about 3 months to develop Shade-V9.V8 to the point where each could run SPEC89.

Generally Shade generates a short sequence of V8 instructions for each V9 instruction. Notable exceptions to this are the 64-bit multiply and divide operations, which Shade compiles as calls to simulation functions. Figure 12 shows the translation body fragment for a V9 add instruction.

V9's 64-bit registers are simulated with V8 register pairs. This doubles the virtual state structure memory traffic. Additional traffic results from being able to simultaneously represent only half as many target machine application registers with the same number of host scratch registers.<sup>11</sup>

<sup>11.</sup> Shade-V9.V8 may thus be starved for registers. On register-intensive translations, using save and restore within translations could alleviate some register pressure problems.

| (     |                      |

|-------|----------------------|

| ldd   | [%vs + vs_r1], 10    |

| ldd   | [%vs + vs_r2], 12    |

| addcc | 11, 13, 15 ! add lsw |

| addx  | 10, 12, 14 ! add msw |

| std   | 14, [%vs + vs_r3]    |

| inc   | 4, %vpc              |

|       | ,                    |

Figure 12. Shade-V9.V8 translation body

V9 SPARC has two sets of condition codes. Each instruction that sets integer condition codes sets one set based on the low order 32 bits of the result (just as in V8), and another based on the full 64 bits of the result. The host integer condition codes are often required (as in the add example above) to simulate 64-bit operations which themselves do not involve condition codes. All this keeps the shade\_[gs]etcc functions very busy.

For these reasons, wide registers and more condition codes, Shade-V9.V8 is less efficient than Shade-V8.V8, and less efficient for integer than floating point applications. On average, Shade-V9.V8 simulates V8 (*sic*) integer SPEC89 benchmarks 12.2 times slower than they run native, and V8 floating point SPEC89 benchmarks 3.3 times slower. Shade-V8.V8 simulates these same benchmarks 6.2 and 2.3 times slower than they run native, respectively.

V9 supports more floating point registers and floating point condition codes than V8. As compilers take advantage of these, Shade-V9.V8's floating point simulation performance will decline.

In V9, memory addresses for floating point doubleword and quadword loads and stores need only be word aligned, whereas in V8 they must be doubleword and quadword aligned. So these operations are simulated by breaking them down into word operations.

In V9, the floating point condition codes may be used by a conditional branch instruction immediately following the floating point compare instruction which set them. In V8, the floating point compare and branch instructions must be separated by at least one other instruction. Shade-V9.V8 sometimes generates a nop instruction following the floating point compare instruction; usually Shade generates other simulation or tracing code that makes this unnecessary.

Programs may manipulate 64-bit pointers under Shade-V9.V8, but when it comes time to actually access memory (load, store, register indirect jump, system call), Shade-V9.V8 ignores the upper 32-bits of the memory address. It can do this since by construction the application only has access to the the lower 4GB of virtual memory. To catch application addressing bugs, Shade-V9.V8 could test the upper 32 address bits to make sure they are zero, but doesn't. Shade-V9.V8 will run slower if and when it needs to simulate a full 64-bit address space.

The host kernel has a 32-bit interface. Only the low order 32 bits of parameters are passed to system calls, and the upper 32 bits of return values are cleared.<sup>12</sup> Note that the SunOS 4.x kernels indicate success/failure via the integer condition codes which user code interfaces interpret to return a 64-bit -1 on failures. Structures (e.g. sigcontext) passed to/from the kernel through memory are more problematic.

Shade provides two options to support simulation of both 32-bit and 64-bit binaries. The first option selects the size (32 or 64 bits) of integers and pointers as they appear in the initial stack. This affects the application runtime startoff code, which may let the effects spread to main and environ. The second option specifies the width (32 or 64 bits) of the stack register save area for save and restore instructions. This affects the stack frame layout.

<sup>12.</sup> In rare cases (e.g. the pathconf system call), sign extending the return value from 32 to 64 bits may be preferable to zero extending it.

# 6. Shade-X.Y

The previous sections describe the specific implementation of Shade for a few target systems and one host system. This section considers what is needed to build a general "Shade-X.Y," namely a Shade-like simulation and tracing tool that simulates target system X on host system Y. Unless explicitly stated otherwise, the implementation techniques presented in this section have not been used in the current Shade implementations.

## 6.1. The Architecture of Shade

Shade is a virtual machine implemented using a lazy incremental compiler. The retargeting issues are the same as for a regular compiler, with the additional requirement that code needs to be produced quickly in order for the system to be effective.